HyperEnclave内存管理模块源码与原理分析

HyperEnclave内存管理模块源码与原理分析

XRHyperEnclave内存管理模块源码与原理分析

目录

- 概述

- 第一层:物理内存管理 (

frame.rs) - 第二层:虚拟地址与权限 (

addr.rs,mod.rs) - 第三层:页表核心机制 (

paging.rs) - 第四层:高级内存映射 (

mm.rs,mapper.rs) - 第五层:Enclave可转换内存管理 (

cmr.rs) - 内存访问流程和地址转换架构

- 总结

1. 概述

项目源码:https://github.com/asterinas/hyperenclave

紧接上一篇《HyperEnclave启动和初始化流程》,我们继续一起学习HyperEnclave。这次我们主要看的是HyperEnclave的内存管理的设计与实现。这个可能是HyperEnclave中最关键的部分了。

设计哲学

HyperEnclave的内存管理模块是其安全性的基石。它的设计哲学是分层抽象和安全隔离。通过将物理内存管理、页表机制和高级内存映射分离开来,实现了清晰、可维护且安全的代码结构。

那最终目标就是为每个Enclave提供一个完全独立、受硬件保护的加密地址空间。

模块结构

我们看src/memory包,就可以发现模块文件及其职责的组织体现了分层思想:

- 底层物理

frame.rs: 物理内存页帧的分配与回收。

- 核心虚拟化

addr.rs: 基础地址类型的定义与转换。paging.rs: 虚拟内存的核心,实现多级页表。

- 高层抽象

mm.rs&mapper.rs: 将页表和物理帧组合成易于使用的内存映射API。

- 专用功能

cmr.rs: Enclave安全页缓存(EPC)的特殊管理。heap.rs: Hypervisor自身的堆内存。gaccess.rs: 安全的Guest内存访问接口。

2. 第一层:物理内存管理 (frame.rs)

这是最底层,负责管理Hypervisor拥有的所有物理内存。

核心数据结构

1 | // src/memory/frame.rs:35-45 |

FrameAllocator: 全局唯一的物理帧分配器,使用bitmap_allocator库(一个位图分配器)来跟踪哪些4K物理页帧是空闲的。Frame: 代表一个或多个连续的、已分配的物理页帧。它是一个所有权句柄,当Frame对象被drop时,其占用的物理内存会自动释放。

分配与释放

1 | // src/memory/frame.rs:60-85 |

alloc在位图中找到一个空闲位,将其标记为已使用,并计算出对应的物理地址返回。dealloc则执行相反操作。

底层原理

这一层不涉及虚拟地址或CPU特性,它仅仅是对一块物理内存进行软件层面的簿记(bookkeeping)。你可以把它想象成一个简化的malloc/free,但操作对象是固定大小(4KB)的物理内存页帧。

3. 第二层:虚拟地址与权限 (addr.rs, mod.rs)

这一层定义了内存操作的基础单位和规则。

地址空间定义

1 | // src/memory/addr.rs:18-25 |

通过类型别名区分了不同上下文中的地址,增强了代码的可读性和安全性(挺有意思的)

地址转换与加密

HyperEnclave中存在两种不同的地址转换机制,以及一种地址加密标记机制:

场景一:Hypervisor自身内存的线性地址转换

对于Hypervisor自身代码和数据的内存,它采用的是一种简单的线性映射。

1 | // src/memory/addr.rs:27-32 |

实现原理:

PHYS_VIRT_OFFSET: 这是一个在Hypervisor启动时计算好的固定偏移量,代表了Hypervisor的虚拟地址基址 (HV_BASE) 和它在物理内存中的加载地址之间的差值。- 转换过程:

virt_to_phys函数用虚拟地址减去这个固定的偏移量,从而得到物理地址;phys_to_virt则执行相反操作,并且过滤掉SME的C-bit。

使用场景: 这种方法仅用于Hypervisor自身的地址空间,因为它简单、高效,并且Hypervisor的内存布局在启动后是固定的。

场景二:Guest虚拟机的通用地址转换

对于Guest的虚拟地址空间(包括Enclave),情况要复杂得多,因为它需要支持任意的、非线性的映射。这依赖于多级页表机制。

关键接口:

1 | // src/memory/paging.rs:217-230 |

这种地址转换通过多级页表遍历实现,详细机制将在第三层(页表核心机制)中详细介绍。

物理地址的硬件加密标记

除了地址转换,HyperEnclave还提供了地址加密标记功能:

1 | // src/memory/addr.rs:35-37 |

注意: 这不是地址转换,而是地址加密标记。phys_encrypted 函数的作用是为一个物理地址启用硬件内存加密。它通过在物理地址上设置一个特殊的标志位(C-bit),告诉CPU的内存控制器对该地址的访问进行加解密操作。

AMD SME (Secure Memory Encryption): 这是AMD处理器提供的一项硬件安全功能。当启用SME后,CPU的内存控制器会在数据离开CPU芯片写入内存时自动加密,在数据从内存读入CPU时自动解密。

C-bit (Encryption Bit): AMD在物理地址总线上增加了一个额外的位,称为C-bit(Crypto-bit)。如果一个物理地址的C-bit被设置为1,内存控制器就会对该地址的访问执行加解密操作。

内存权限标志

1 | // src/memory/mod.rs:45-60 |

- 底层原理:

MemFlags中的每一位都直接对应x86-64页表项(PTE)中的一个控制位。例如:READ|WRITE对应R/W(Read/Write) 位。EXECUTE对应XD(Execute Disable) 位(逻辑相反)。USER对应U/S(User/Supervisor) 位。

当创建页表项时,这些标志位会被组合并写入PTE的硬件结构中,由CPU的MMU强制执行。

4. 第三层:页表核心机制 (paging.rs)

这是内存虚拟化的核心,实现了将虚拟地址翻译成物理地址的机制。

核心抽象:GenericPTE

1 | // src/memory/paging.rs:166-203 |

这个trait是HyperEnclave页表实现的精髓。它定义了一个页表项(PTE)必须具备的通用行为,将上层逻辑与具体硬件(如Intel EPT或AMD NPT)的PTE格式解耦。

数据结构:Level4PageTable

HyperEnclave使用一个4级页表结构来管理地址空间,这与x86-64架构相匹配。

1 | // src/memory/paging.rs:691-696 |

地址转换机制详解

HyperEnclave的地址转换是通过多级页表遍历实现的,这是现代操作系统内存管理的核心。

虚拟地址索引提取

首先,系统需要从64位虚拟地址中提取各级页表的索引:

1 | // src/memory/paging.rs:865-880 |

地址分解原理:

- x86-64的64位虚拟地址被分为5个部分:

- [63:48]: 符号扩展位(必须与第47位相同)

- [47:39]: L4页表索引(9位,512个条目)

- [38:30]: L3页表索引(9位,512个条目)

- [29:21]: L2页表索引(9位,512个条目)

- [20:12]: L1页表索引(9位,512个条目)

- [11:0]: 页内偏移(12位,4KB页面)

页表遍历核心逻辑

1 | // src/memory/paging.rs:280-318 |

地址查询接口

1 | // src/memory/paging.rs:217-230 |

query函数的实现:

1 | // src/memory/paging.rs:406-420 |

地址转换完整流程

- 起始点: 从根页表(L4 Table)开始,根地址存储在

self.root_paddr()中 - L4遍历: 使用虚拟地址的

[47:39]位作为索引,在L4页表中找到L4 PTE - L3遍历: 如果L4 PTE不是叶子节点,使用

[38:30]位在L3页表中查找 - L2遍历: 如果L3 PTE不是叶子节点,使用

[29:21]位在L2页表中查找 - L1遍历: 如果L2 PTE不是叶子节点,使用

[20:12]位在L1页表中查找 - 最终地址: PTE的基址 + 虚拟地址的低12位(页内偏移)= 最终物理地址

底层原理:MMU与CR3

query函数是在软件中模拟了CPU硬件MMU(内存管理单元)的工作流程。在真实运行时,Hypervisor通过

activate()方法将根页表的物理地址加载到CR3寄存器中。1

2// 伪代码,实际由x86_64库提供

asm!("mov cr3, {}", in(reg) root_paddr);之后,每一次内存访问,CPU的MMU都会自动、硬件级地执行上述

query函数中的页表遍历过程,以极高的速度完成地址翻译。如果翻译失败(例如PTE的Present位为0),MMU会触发一个Page Fault异常,将控制权交还给Hypervisor的处理程序。

总结

PTE的核心作用:

- 地址映射: 记录虚拟地址到物理地址的映射关系

- 权限控制: 记录内存页面的访问权限(读/写/执行/用户/加密等)

- 状态管理: 记录页面状态(是否存在、是否被访问、是否为大页等)

- 硬件接口: 作为软件与CPU硬件MMU之间的数据结构

这块如果你之前不是很了解 linux 的 MMU 或者不太清楚 HyperEnclave的宏观地址转换架构(这个文章后面会说),直接说细节可能很难理解透。

5. 第四层:高级内存映射 (mm.rs, mapper.rs)

这一层提供了面向开发者的、更易于使用的API,将物理帧分配和页表操作封装在一起。

核心数据结构

1 | // src/memory/mm.rs:35-42 |

MemorySet代表一个完整的地址空间(如一个Enclave的地址空间)。它包含一个页表(pt)和多个MemoryRegion。MemoryRegion定义了一个连续的虚拟内存区域及其属性。

核心逻辑:MemorySet::insert

1 | // src/memory/mm.rs:85-94 (simplified) |

self.pt.map(®ion)是关键,它内部会:

- 遍历

region中的每一个虚拟页面。 - 为每个虚拟页面调用

frame::alloc()分配一个物理帧。 - 计算出PTE应该在页表中的位置。

- 创建一个PTE,将虚拟页面链接到分配的物理帧,并设置好

region.flags中指定的权限。

底层原理:从API到硬件

一个MemorySet::insert调用最终会转化为一系列底层的CPU操作:

- 软件簿记:更新

FrameAllocator的位图。 - 内存写操作:修改多级页表中的PTE内容。

- TLB刷新:执行

invlpg指令使TLB(快表)中的旧缓存失效,确保CPU使用最新的页表映射。

6. 第五层:Enclave可转换内存管理 (cmr.rs)

这是HyperEnclave最具特色的部分,专门用于管理Enclave的安全内存(EPC)。

设计思想:可转换内存

HyperEnclave不静态划分普通内存和安全内存,而是提出可转换内存(Convertible Memory)的概念。这意味着一块物理内存页可以在运行时被动态地转换为普通内存、EPC安全内存或Hypervisor内部内存。

核心数据结构

1 | // src/memory/cmr.rs:59-71 |

ConvMemManager为系统中每一页可转换的物理内存维护一个CmrmEntry元数据。这个巨大的元数据数组就是CMRM(Convertible Memory Region Metadata)。CmrmEntry的核心是page_status,它记录了对应物理页的当前类型。

核心逻辑:initialize_cmrm

1 | // src/memory/cmr.rs:172-210 |

此函数在Hypervisor启动时被调用,它遍历所有可转换内存,根据固件提供的信息(如哪些内存预留为初始EPC),为每个物理页设置其初始PageStatus。

底层原理:安全内存的实现

将一页普通内存转换为EPC安全内存的完整流程是:

- 软件层:调用

ConvMemManager的接口,将对应CmrmEntry的page_status从Normal更新为Secure。 - 页表层:找到映射到该物理页的PTE,并将其

MemFlags添加ENCRYPTED标志。 - 地址转换层:在构建最终PTE时,

phys_encrypted函数会为该物理地址设置C-bit。 - 硬件层:当MMU使用这个PTE进行地址翻译时,它将带有

C-bit的物理地址发送到内存控制器。内存控制器识别到C-bit后,自动使用SEV引擎对该次内存访问进行加解密。

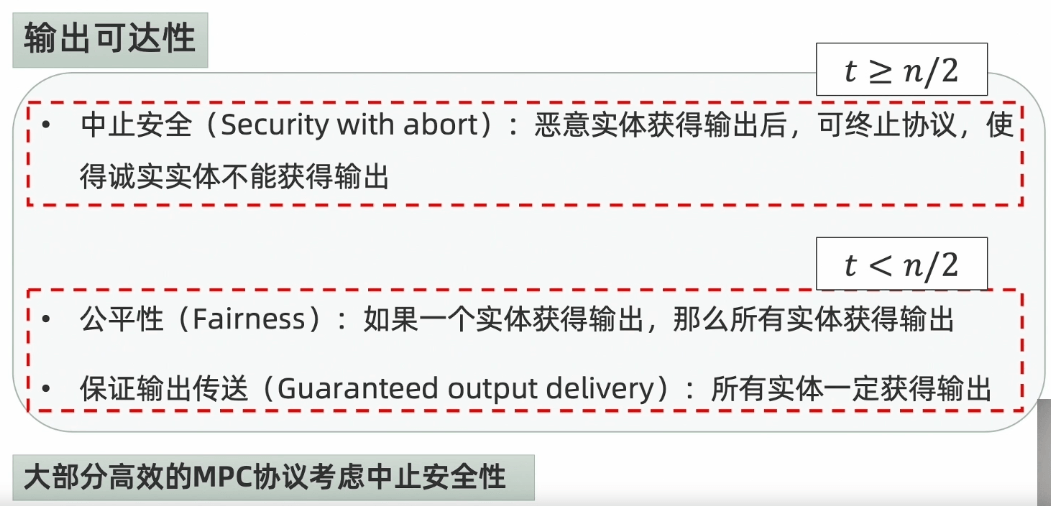

7.内存访问流程和地址转换架构

graph TD

subgraph "Guest程序内存访问"

A1[Guest应用程序] --> A2[Guest虚拟地址]

A2 --> A3[Guest页表遍历]

A3 --> A4[Guest物理地址]

A4 --> A5[Nested页表/EPT]

A5 --> A6[实际物理内存]

end

subgraph "Enclave程序内存访问"

B1[Enclave应用程序] --> B2[Enclave虚拟地址]

B2 --> B3[Enclave Guest页表遍历]

B3 --> B4[Guest物理地址]

B4 --> B5[Nested页表/EPT]

B5 --> B6[实际物理内存]

end

subgraph "控制层次"

C1[Guest操作系统] --> C2[管理Guest页表]

C3[HyperEnclave] --> C4[管理Enclave Guest页表]

C3 --> C5[管理Nested页表]

C3 --> C6[安全策略控制]

end

7.1 Guest程序的内存访问机制

地址转换流程

从代码分析可以看出,Guest程序的内存访问分为两种情况:

普通Guest内存访问(NonSecure)

1 | // src/memory/gaccess.rs:215-227 |

转换步骤:

- Guest虚拟地址 → Guest页表查询 → Guest物理地址

- Guest物理地址 → Nested页表(EPT/NPT)→ 实际物理内存

页表遍历机制

Guest页表遍历通过四级页表结构实现:

1 | // src/memory/paging.rs:865-880 |

7.2. Enclave程序的内存访问机制

特殊的地址转换

Enclave程序的内存访问更复杂,需要额外的安全检查:

1 | // src/memory/gaccess.rs:231-235 |

Enclave页面加载机制

1 | // src/enclave/mod.rs:967-1009 |

转换步骤:

- Enclave虚拟地址 → Enclave Guest页表查询 → Guest物理地址

- Guest物理地址 → Nested页表(EPT/NPT)→ 实际物理内存

- 额外安全检查:EPCM验证、权限检查、状态验证

7.3. 控制层次分析

7.3.1 Guest操作系统控制范围

Guest操作系统(Linux)控制的内容:

1 | // 从代码推断Guest OS的控制范围 |

Guest OS控制:

- Guest页表管理:创建、修改、删除Guest虚拟地址到Guest物理地址的映射

- 内存分配:在Guest物理地址空间内分配内存给应用程序

- 权限管理:设置页面的读写执行权限(受限)

- 进程隔离:在Guest内部实现进程间的内存隔离

Guest OS无法控制:

- Nested页表(EPT/NPT)

- Enclave的内存管理

- 实际物理内存的分配

- 跨Guest的安全策略

7.3.2 HyperEnclave控制范围

从代码可以看出HyperEnclave的全面控制:

1 | // src/cell.rs:27-36 |

HyperEnclave控制:

1)Nested页表管理

- 二级地址转换:Guest物理地址 → 实际物理地址

- 内存隔离:确保不同Guest无法访问对方内存

- 访问权限:控制Guest对物理内存的访问权限

2)Enclave专用管理

1 | // src/enclave/mod.rs:170-175 |

- Enclave Guest页表:专门为Enclave创建的页表

- EPCM管理:Enclave页面缓存映射管理

- 安全策略:实施Enclave的安全隔离策略

3)内存安全验证

1 | // src/memory/gaccess.rs:140-158 |

- 地址验证:验证访问的物理地址是否合法

- 安全边界:强制执行安全内存和非安全内存的边界

- 访问控制:根据上下文控制内存访问权限

7.4 内存访问的完整流程图

Guest程序内存访问

sequenceDiagram

participant App as Guest应用

participant OS as Guest OS

participant HV as HyperEnclave

participant HW as 硬件MMU

App->>HW: 访问虚拟地址

HW->>OS: 查询Guest页表

OS->>HW: 返回Guest物理地址

HW->>HV: 查询Nested页表

HV->>HW: 返回实际物理地址

HW->>App: 完成内存访问

Enclave程序内存访问

sequenceDiagram

participant EApp as Enclave应用

participant HV as HyperEnclave

participant EPCM as EPCM管理器

participant HW as 硬件MMU

EApp->>HW: 访问Enclave虚拟地址

HW->>HV: 查询Enclave Guest页表

HV->>EPCM: 验证页面状态和权限

EPCM->>HV: 返回验证结果

HV->>HW: 返回Guest物理地址

HW->>HV: 查询Nested页表

HV->>HW: 返回实际物理地址

HW->>EApp: 完成内存访问

关键差异总结

| 特性 | Guest程序 | Enclave程序 |

|---|---|---|

| 页表管理 | Guest OS管理 | HyperEnclave管理 |

| 安全检查 | 基本权限检查 | EPCM + 权限 + 状态验证 |

| 内存区域 | 普通物理内存 | EPC(加密页面缓存) |

| 隔离级别 | 进程级隔离 | 硬件级加密隔离 |

| 故障处理 | 标准页面错误 | 特殊安全异常 |

| 动态管理 | OS内存管理 | HyperEnclave + EPCM |

这种设计确保了Enclave程序具有比普通Guest程序更强的安全保障,同时HyperEnclave通过控制关键的页表结构和安全策略,实现了对整个系统内存访问的全面管控。

8. 总结

HyperEnclave的内存管理是一个设计精良、层次分明的系统。

- 它从最底层的物理帧位图开始。

- 通过多级页表和PTE抽象,构建了强大的虚拟内存机制。

- 利用**

MemorySet**将其封装成易用的高级API。 - 最后通过创新的可转换内存模型(CMRM),实现了对EPC安全内存的灵活、动态管理。

整个系统的实现深度依赖于对x86-64硬件特性(如MMU、CR3、MSR、SEV加密位)的直接利用,并通过Rust的类型系统和抽象能力,将这些复杂的底层操作安全、清晰地组织起来。